Hdl Design Flow

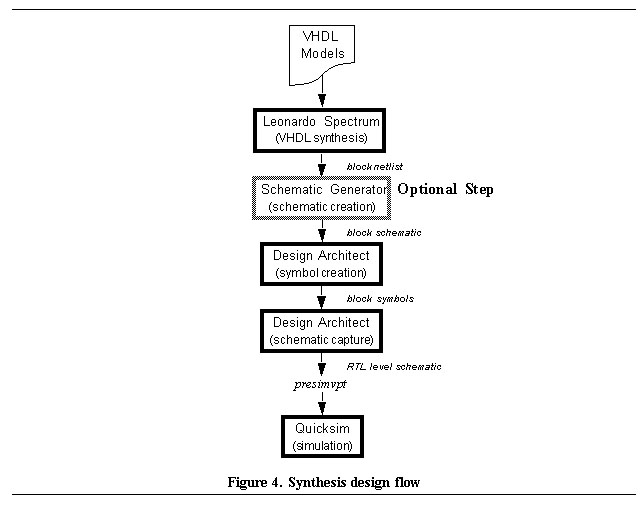

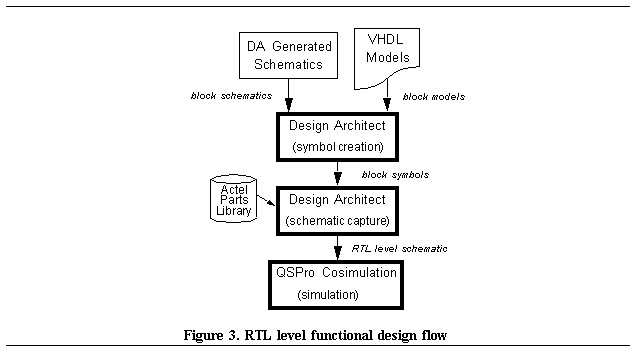

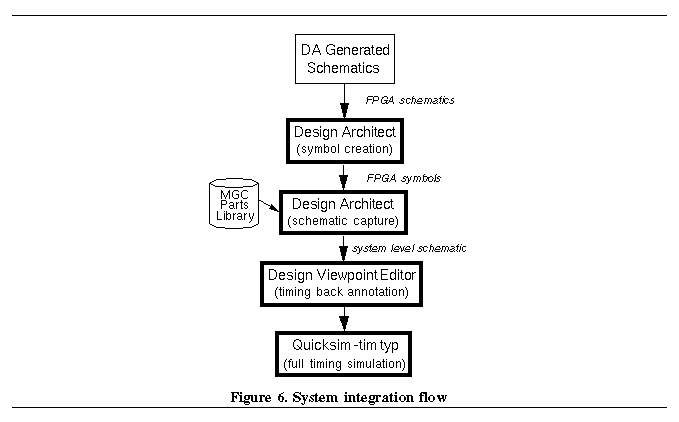

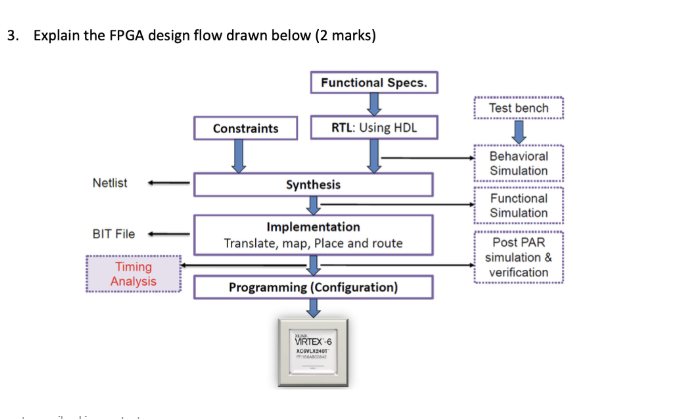

In general as the design flow progresses toward a physically realizable form the design database becomes progressively more laden with technology specific information which cannot be stored in a generic hdl description.

Hdl design flow. It means by using a hdl we can describe any digital hardware at any level. Designs which are described in hdl are independent of technology very easy for designing and debugging and are normally more useful than schematics particularly for large circuits. The so called front end begins with figuring out the basic approach and building blocks at the block diagram level. Unified modeling language is the most widely used example for software design.

Verilog supports a design at many levels of abstraction. Through hardware description language or hdl or you may even combine the two and use a best of both worlds approach using tools that can convert hdl into schematics and vice versa depending on your fpga design and preference. The use of flow based design tools allows for more holistic system design and faster development. C to hdl tools and flow have a similar aim but with c or c like programming languages.

Design flow there are several steps in an hdl based design process often called the design flow. Hdl design house may then use and or share this de personalized information with third parties to improve our services. Verilog hdl was designed by phil moorby who was later to become the chief designer for verilog xl and the first corporate fellow at cadence design systems. The company was privately held at that time by dr.

Hdl designer combines deep analysis capabilities advanced creation editors and complete project and flow management to deliver a powerful hdl design environment that increases the productivity of individual engineers and teams local or remote and enables a repeatable and predictable design process. The next section will present an overview of the design flow and the following section will illustrate the design flow in more detail using an example. These steps are applicable to any hdl based design process. Verilog hdl originated at automated integrated design systems later renamed as gateway design automation in 1985.

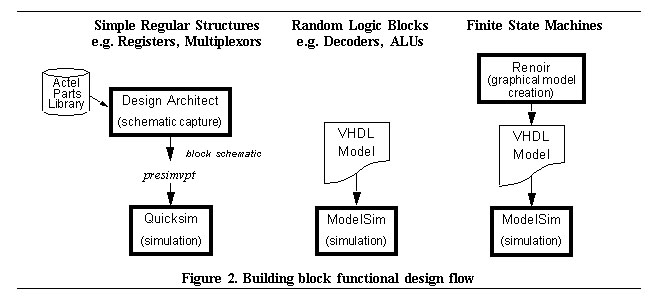

Prabhu goel the inventor of the podem test generation algorithm. The major three are. Ema1997 general design flow i 13 of 24 rtl and behavioral design behavioral synthesis a gap between domain specific tools and rtl synthesis tools a higher level of abstraction for the designer to logic synthesis hdl design flow initial model in c or c or simulation vhdl define and test the functional aspects of the design. Hdl design house may de personalize personal information by removing personally identifiable characteristics such as name and email address and aggregate data for use in surveys or other business purposes.

1 draw the design flow of vhdl and explain each block.